## электронный научно-технический журнал

# **ИНЖЕНЕРНЫЙ ВЕСТНИК**

Издатель ФГБОУ ВПО "МГТУ им. Н.Э. Баумана". Эл No. ФС77-51036. ISSN 2307-0595

## Сравнение архитектур микропроцессоров класса ARM

# 04, апрель 2014

УДК: 004.3

авторы: Королев Б. Ю., Хартов В. Я.

khartovbmstu@gmail.com

Россия, МГТУ им. Баумана

## 1. История развития архитектуры ARM

Архитектура ARM разрабатывается фирмой ARM Holdings (ранее называлась Advanced RISC Machines). Первый процессор с архитектурой ARM был выпущен в 1985 году. В процессе развития и усовершенствования архитектуры фирма ARM представила пользователям целый ряд модификаций ядра, образующих семейства [1].

В наши дни 32-разрядная ARM — наиболее широко используемая архитектура процессоров для мобильных устройств, и наиболее популярная архитектура 32-разрядных процессоров для встраиваемых систем [2].

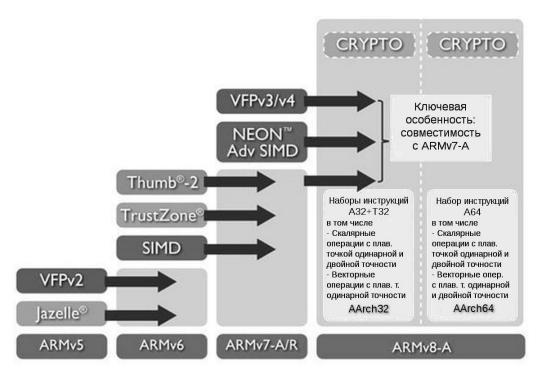

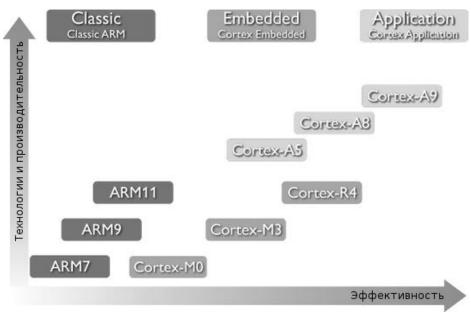

В настоящее время архитектуру ARM представляют два класса: «классические» процессоры, куда входят семейства ARM7, ARM9 и ARM11, и семейство Cortex, разделяемое на три «профиля» Cortex-A, Cortex-R и Cortex-M. На рис. 1 представлена диаграмма, иллюстрирующая развитие архитектуры ARM от поколения к поколению

## . 2. Особенности архитектуры ARM

Архитектура ARM представляет собой разновидность архитектуры RISC, которую характеризуют [3]:

- однородный регистровый файл;

- обработка производится только регистровых данных, а обмен с памятью осуществляется специальными командами (load/store);

- разнообразные способы адресации.

Процессоры с архитектурой ARM демонстрируют удачное сочетание высокой производительности, небольшого размера кода, низкого энергопотребления при небольшой занимаемой площади на кристалле.

**Рис.1**. Эволюция архитектуры ARM

## Набор инструкций ARM.

ARM имеет набор инструкций с длиной инструкции 32 бита. Инструкции выравниваются по границам в 4 байта. Характерной особенностью команд ARM является то, что практически все они могут выполняться условно, т. е. в зависимости от состояния процессора в результате предыдущей операции обработки данных. Если условие не выполняется, команда обрабатывается как пустая команда. Такой подход позволяет кодировать небольшие группы операторов if и while без использования инструкций ветвления и повышает эффективность работы процессорного конвейера.

## Набор инструкций Thumb.

Набор инструкций Thumb представляет подмножество наиболее часто используемых инструкций ARM, упакованных в 16-битовый формат. Во время выполнения они на лету и без потерь транслируются в полноценные ARM-инструкции. Благодаря этому набор Thumb обеспечивает:

- высокую плотность кода для сокращения необходимого объёма памяти и стоимости системы;

- производительность 32-битового режима в сочетании с 8- или 16-битовой памятью и/или шиной, что снижает стоимость системы;

- низкое энергопотребление и большее время работы от батареи;

- меньшую площадь на кристалле.

Разработчик приложения может сочетать наборы команд ARM и Thumb, по мере надобности отдавая приоритет производительности или объёму кода.

Thumb-2 — развитие набора команд Thumb. Это набор инструкций смешанной длины (16- и 32-битовых), сочетающий положительные качества ARM и Thumb. Thumb-2 обратно совместим с ARM и Thumb.

## 3.Семейство «классических» процессоров ARM

#### 3.1. ARM7

Семейство ARM7 было представлено в 1994 году и завоевало огромную популярность. Фактически, с него началось массовое распространение ARM-процессоров. Во многом, это произошло благодаря процессору ARM7TDMI.

ARM7TDMI (ARM7 + 16-битовый **T**humb + отладка по JTAG + fast **M**ultiplier + enhanced **I**CE) — это 32-разрядное RISC-ядро с трёхступенчатым конвейером (Fetch-Decode-Execute) и архитектурой фон Неймана. Долгое время это ядро было наиболее широко используемым среди процессоров ARM. На его основе был разработан Nokia 6110, первый GSM сотовый телефон.

ARM7TDMI содержит несколько значительных усовершенствований по сравнению с предшественниками:

- набор инструкций Thumb,

- поддержка стандарта JTAG и модуль EmbeddedICE для внутрисхемной отладки программ,

- поддержка операций умножения с 64-разрядным результатом.

Также в семействе ARM7 была представлена технология Jazelle — аппаратное ускорение исполнения байт-кода Java.

## 3.2. ARM9

Следующим семейством процессоров стало семейство ARM9. Основные отличия от ARM7 [4]:

- переход на гарвардскую архитектуру с разделёнными кэшами команд и данных;

- снижение энергопотребления и риска перегрева;

- переход на пятиступенчатый конвейер (Fetch Decode Execute Memory Writeback) позволил увеличить тактовую частоту почти вдвое при той же технологии;

- усовершенствование выполнения команд, в частности

- ускорение операций загрузки и выгрузки,

- оптимизация конвейера и устранение взаимоблокировок в нём;

- поддержка расширений «Enhanced DSP instructions» для более эффективного выполнения алгоритмов обработки сигналов;

контроллер памяти с поддержкой виртуальной памяти (MMU) или функций защиты памяти (MPU).

#### 3.3. ARM11

Архитектура ARM11 появилась в 2002 г. Процессоры с ядром ARM11 используются в смартфонах Apple, Nokia и др.

Отличия от ARM9 [5]:

- первый многоядерный процессор ARM11 MPCore;

- инструкции ОКМД, позволяющие ускорить обработку видео- и аудиоданных;

- появление физически адресуемого кэша L1;

- поддержка адресации данных без выравнивания и со смешанным порядком байтов;

- усовершенствованный конвейер, включая

- восемь ступеней,

- переупорядочивание команд,

- динамическое предсказание переходов,

- параллельное выполнение операций загрузки/выгрузки и операций в АЛУ;

- возможность пересылки 64-битовых слов;

- поддержка набора инструкций Thumb-2 (в процессоре ARM1156T2-S);

- усовершенствованная система отладки.

Также в процессорах семейства ARM11 впервые представлена технология TrustZone [6], позволяющая разрабатывать системы, более стойкие к угрозам безопасности со стороны программного обеспечения. Технология позволяет одному процессорному ядру исполнять код в двух контекстах, обычном и защищённом, и переключаться между ними, используя специальный режим процессора Monitor.

#### 4. Семейство процессоров Cortex

#### 4.1 Профили процессоров Cortex

Семейство Cortex подразделяется на три так называемых профиля:

- Cortex-A (Application) высокопроизводительные процессоры для ресурсоёмких областей применения, таких как смартфоны, телевизоры, промышленные сетевые устройства и серверы;

- Cortex-R (Real-time) высокопроизводительные процессоры для встраиваемых систем, где основными требованиями являются надёжность, отказоустойчивость и время реакции (например, медицинское оборудование, модули беспроводной связи, цифровые камеры, автомобильные управляющие системы);

— Cortex-M (MCU) — ядра для микроконтроллеров и приложений, где требуются низкая стоимость и энергопотребление, а также обработка сигналов (например, измерительные устройства, интерфейсы, автомобильные и промышленные системы управления, медицинское оборудование).

#### 4.2 Cortex-A и Cortex-R

Cortex-A и Cortex-R — это усовершенствованные высокопроизводительные процессорные ядра. Наиболее значимые свойства [7]:

- полная поддержка системы команд Thumb-2;

- необязательные инструкции Security Extensions;

- поддержка иерархического кэша;

- различные модели памяти формализованы (используется один из двух профилей памяти):

- профиль ARMv7-A использует Virtual Memory System Architecture (VMSA) с поддержкой виртуальной памяти;

- профиль ARMv7-R использует Protected Memory System Architecture (PMSA) с поддержкой защищённой памяти;

- расширение NEON поддержка инструкций векторной обработки данных (ОКМД) с использованием отдельного конвейера и регистрового файла;

- поддержка технологии big.LITTLE, позволяющая совместно использовать пару из высокопроизводительного и энергосберегающего процессоров для достижения одновременно высокой производительности и низкого потребления.

## 4.3 Cortex-M

Ядра Cortex-М представляют собой развитие архитектуры ARM для приложений, в которых размер кода и детерминированность операций являются более важными характеристиками, чем производительность. Cortex-М значительно отличается как от «классических» семейств, так и от других профилей Cortex.

Основное отличие заключается в программной модели процессора и способе обработки исключений.

В Cortex-M [8] определяются два состояния процессора: Thread и Handler, и два способа выполнения кода — привилегированный и непривилегированный. В режиме Handler код всегда исполняется как привилегированный. Используются два указателя стека Main и Process. Указатель Process может быть использован только в режиме Thread, Main — в обоих режимах.

Процессор имеет встроенный контроллер прерываний. Исключительные ситуации делятся на 4 категории: перезагрузка, системный вызов, ошибка и прерывание. Каждое исключение имеет

номер, приоритет и вектор-адрес обработчика. При обработке исключений для ускорения операций используется:

- приоритетное обслуживание (прерывание обработки при возникновении исключения с более высоким приоритетом);

- аппаратное сохранение/восстановление контекста с коррекцией адреса возврата (не нужно делать коррекцию вручную, как в ранних поколениях ARM)

- сцепление обработчиков подавление процедуры восстановления контекста, если ожидается ещё один обработчик исключения;

- прерывание восстановления контекста, если в этот момент приходит следующий запрос прерывания;

- «позднее прибытие» (если запрос с более высоким приоритетом приходит во время переключения контекста на обработчик запроса с меньшим приоритетом, то по окончании переключения контекста сразу же запускается обработчик высокоприоритетного прерывания).

Другие особенности Cortex-M:

- поддерживается только один порядок байтов для кода (little endian);

- поддерживается только набор инструкций Thumb;

- нет поддержки ОКМД-инструкций;

- поддерживается ограниченный набор инструкций загрузки/выгрузки.

#### 5. Новая архитектура ARMv8 и Cortex-A50

В конце 2011 г. была представлена новая версия архитектуры, ARMv8. В ней определяется новые режимы работы ядра, AArch64 с набором команд A64 и AArch32, совместимый с предыдущими версиями архитектуры ARM (наборы команд ARM и Thumb получают названия соответственно A32 и T32). Основные особенности A64 [9,10]:

- сохранение семантики инструкций из AArch32;

- 31 постоянно доступных 64-битовых регистров;

- регистры общего назначения не банкируются;

- счётчик инструкций (PC) и указатель стека (SP) выделены из регистров общего назначения;

- специальный нулевой регистр, доступный для большинства инструкций.

Основные отличия от А32:

- поддержка 64-битовых операндов;

- работа с 64-битовыми адресами;

- меньшее количество условных инструкций, чем в AArch32;

- вычисления с плавающей запятой в режиме ОКМД с двойной точностью;

- новые операции с плавающей запятой в соответствии с IEEE754-2008.

Подобную архитектуру имеют процессоры Cortex-A50.

## **6.**Сравнение производительности ядер ARM

В табл.1 приводятся оценки производительности ядер ARM в MIPS, DMIPS (по тесту Dhrystone), MIPS/МГц и типичные рабочие частоты процессоров [11-27].

**Таблица 1.** Производительность ядер процессоров класса ARM

| Семейство | Ядро           | Кэш (I / D), MMU                                     | Производи-<br>тельность/<br>частота,<br>MIPS/МГц                       |

|-----------|----------------|------------------------------------------------------|------------------------------------------------------------------------|

| ARM7      | ARM710a        | 8 КБ общий                                           | 40 МГц<br>0,68 DMIPS/МГц                                               |

| ARM7TDMI  | ARM7TDMI(-S)   | нет                                                  | 15 MIPS @<br>16,8 ΜΓμ<br>63 DMIPS @<br>70 ΜΓμ                          |

|           | ARM710T        | 8 КБ общий, MMU                                      | 36 MIPS @<br>40 МГц                                                    |

|           | ARM720T        | 8 КБ общий, MMU,<br>FCSE*                            | 60 MIPS @<br>59,8 МГц                                                  |

| ARM8      | ARM810         | 8 КБ общий, MMU                                      | 84 MIPS @<br>72 МГц<br>1,16 DMIPS/МГц                                  |

| ARM9TDMI  | ARM920T        | 16 КБ / 16 КБ, ММU,<br>FCSE*                         | 200 MIPS @<br>180 МГц                                                  |

| ARM9E     | ARM926EJ-S     | изменяемый, TCMs**,<br>MMU                           | 220 MIPS @<br>200 МГц                                                  |

| ARM11     | ARM1136J(F)-S  | изменяемый, MMU                                      | 740 @ 532–<br>665 МГц (i.MX31<br>SoC),<br>400–528 МГц                  |

|           | ARM1176JZ(F)-S | изменяемый, MMU,<br>TrustZone                        | 965 DMIPS @<br>772 МГц, до 2;<br>600 DMIPS с 4<br>процессорами         |

| Cortex-M  | Cortex-M0      | нет                                                  | 0,84 DMIPS/MГц                                                         |

|           | Cortex-M0+     | нет, необязательный MPU с 8 областями                | 0,93 DMIPS/MГц                                                         |

|           | Cortex-M1      | нет, 0-1024 КБ<br>I-TCM, 0-1024 КБ<br>D-TCM, без MPU | 136 DMIPS @<br>170 МГц,<br>(0,8 DMIPS/МГц в<br>зависимости от<br>FPGA) |

| Семейство  | Ядро                 | Кэш (I / D), MMU                                                                                       | Производи-<br>тельность/<br>частота,<br>MIPS/МГц                                        |

|------------|----------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Cortex-M   | Cortex-M3            | нет, необязательный MPU с 8 областями                                                                  | 1,25 DMIPS/МГц                                                                          |

|            | Cortex-M4            | нет, необязательный MPU с 8 областями                                                                  | 1,25 DMIPS/МГц                                                                          |

| Cortex-A   | Cortex-A5            | 4-64 K5 / 4-64 K5 L1,<br>MMU + TrustZone                                                               | 1,57 DMIPS / МГц<br>на ядро                                                             |

|            | Cortex-A7 MPCore     | 32 КБ / 32 КБ L1,<br>0-4 МБ L2,<br>MMU + TrustZone                                                     | 1,9 DMIPS / МГц<br>на ядро                                                              |

|            | Cortex-A8            | 16-32 КБ /16-32 КБ L1,<br>0-1 МБ L2, необ. ECC,<br>MMU + TrustZone                                     | до 2000 (2,0<br>DMIPS/МГц на<br>скорости от<br>600 МГц до 1 ГГц<br>и более)             |

|            | Cortex-A12           | 32-64 КБ / 32 КБ L1,<br>256 КБ-8 МБ L2                                                                 | 3,0 DMIPS / МГц<br>на ядро                                                              |

|            | Cortex-A15<br>MPCore | 32 КБ Iw/четность /<br>32 КБ Dw/ECC L1,<br>0-4 МБ L2, L2 с ECC,<br>MMU + TrustZone                     | От<br>3,5 DMIPS/МГц<br>на ядро (до<br>4,01 DMIPS/МГц<br>в зависимости<br>от реализации) |

| Cortex-A50 | Cortex-A53           | 8-64 КБ с чётностью /<br>8-64 КБ с ЕСС L1 на<br>ядро,<br>128 КБ-2 МБ L2общий,<br>40-битные физ. адреса | 2,3 DMIPS/МГц                                                                           |

|            | Cortex-A57           | 48 КБ с DED чётностью / 32 КБ с ECC L1 на ядро, 512 КБ-2 МБ L2общий, 44-битные физ. адреса             | От<br>4,1 DMIPS/МГц<br>на ядро (до<br>4,76 DMIPS/МГц<br>в зависимости<br>от реализации) |

<sup>\* –</sup> Fast Context Switch Extension (расширение быстрого переключения контекста)

<sup>\*\* –</sup> Tightly Coupled Memory (некэшируемая память быстрого доступа) [6]

## 7. Рекомендации по выбору процессоров класса ARM

Каждое семейство процессоров занимает свою нишу в области встраиваемых систем. На рис. 2 отражено положение семейств процессоров в классе ARM в зависимости от их производительности и эффективности.

**Рис. 2**. Сравнение семейств процессоров ARM

Назовем общие рекомендации по выбору процессора:

- если целевая система должна иметь прежде всего высокую производительность, следует выбирать процессоры Cortex-A;

- если основное требование к системе надёжность, отказоустойчивость, тогда следует выбрать процессор Cortex-R;

- если разрабатываемая система должна обрабатывать большие потоки данных или реагировать на большое число событий, следует выбрать процессор семейства Cortex-M, так как он обеспечит наиболее быструю обработку прерываний;

- если целевая система должна быть высокопроизводительной и поддерживать большие объёмы памяти, следует выбрать процессор из семейства Cortex-A50, имеющий соответствующие возможности;

- если к системе не предъявляется жёстких требований по производительности и отзывчивости, можно выбрать процессор из семейства «классических»; ввиду значительного числа уже сделанных на основе этих процессоров разработок систему будет проще спроектировать, используя опыт и, возможно, готовые программные или аппаратные компоненты.

#### Заключение

Проведенный в работе анализ позволяет ориентироваться в многообразии процессоров с архитектурой ARM, понять достоинства и недостатки различных вариантов архитектуры, выявить показания к применению процессоров ARM для решения разных прикладных задач. Интересной для дальнейшего изучения является задача оценки производительности процессоров разных семейств с учётом специфики этих семейств. Традиционные методы оценки на основе тестов, симулирующих работу программ общего назначения, не совсем подходят для этого, потому что лучшие результаты в них будут показывать высокопроизводительные процессоры общего назначения, тогда как во встраиваемых системах часто важны другие характеристики, например, низкое энергопотребление или скорость реакции на события. Появляется потребность в методах оценки производительности процессоров в таких областях применения, и, возможно, комплексной, универсальной оценки, дающей сравнимые показателей достаточной точности для процессоров разных типов.

## Список литературы

- 1. Хартов В.Я. Микропроцессорные системы. М.: Издательский центр «Академия», 2010. 352 с.

- 2. Fitzpatrick, J. An interview with Steve Furber. // Communications of the ACM. 2011. T. 54, № 5. C. 34-39.

- 3. ARM Architecture Reference Manual // ARM Limited. Режим доступа: http://people.freebsd.org/~chuckr/arm/ARMArchitectureRefMan.pdf (дата обращения 12.11.2013).

- 4. ARM9 Technical Reference Manual // ARM Limited. Режим доступа: http://infocenter.arm.com/help/topic/com.arm.doc.ddi0222b/DDI0222.pdf (дата обращения 12.11.2013).

- 5. ARM11 MPCore Processor Technical Reference Manual // ARM Limited. Режим доступа: http://infocenter.arm.com/help/topic/com.arm.doc.ddi0360f/DDI0360F\_arm11\_mpcore\_r2p0\_trm.pdf (дата обращения 12.11.2013).

- 6. TrustZone // ARM Limited. Режим доступа: http://www.arm.com/products/processors/technologies/trustzone/index.php (дата обращения 25.01.2014).

- 7. ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition Issue C // ARM Limited. Режим доступа:

http://iamroot.org/wiki/lib/exe/fetch.php?media=%EC%8A%A4%ED%84%B0%EB%94%94:ddi0406c\_b arm architecture reference manual.pdf (дата обращения 14.11.2013).

- 8. ARMv7-M Architecture Reference Manual // ARM Limited. Режим доступа: http://www.eecs.umich.edu/courses/eecs373/readings/ARMv7-M\_ARM.pdf (дата обращения 14.11.2013).

- 9. ARM Processor Architecture // ARM Limited. Режим доступа: http://www.arm.com/products/processors/instruction-set-architectures/index.php (дата обращения 14.11.2013).

- 10. ARM Architecture Reference Manual ARMv8, for ARMv8-A architecture profile // ARM Limited. Режим доступа: http://www.cs.utexas.edu/~peterson/arm/DDI0487A\_a\_armv8\_arm\_errata.pdf (дата обращения 25.01.2014).

- 11. Guy Larri. ARM810 Dancing to the Beat of a Different Drum // ARM Limited. Режим доступа: http://www.dlhoffman.com/publiclibrary/software/hot\_chips\_papers/hc96/hc8\_pdf/4.1.pdf (дата обращения 14.11.2013).

- 12. VLSI Technology Now Shipping ARM810 // EE Times. Режим доступа: http://www.eetimes.com/document.asp?doc\_id=1208831 (дата обращения 14.11.2013).

- 13. Cortex-M0 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-m/cortex-m0.php?tab=Specifications (дата обращения 14.11.2013).

- 14. Cortex-M0+ Specification Summary // ARM Limited. Режим доступа: http://www.arm.com/products/processors/cortex-m/cortex-m0plus.php (дата обращения 14.11.2013).

- 15. Cortex-M1 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-m/cortex-m1.php?tab=Specifications (дата обращения 14.11.2013).

- 16. ARM Extends Cortex Family with First Processor Optimized for FPGA // ARM Limited. Режим доступа: http://www.arm.com/about/newsroom/17017.php (дата обращения 14.11.2013).

- 17. Cortex-M3 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-m/cortex-m3.php?tab=Specifications (дата обращения 14.11.2013).

- 18. Cortex-M4 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-m/cortex-m4-processor.php?tab=Specifications (дата обращения 14.11.2013).

- 19. Cortex-A5 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-a/cortex-a5.php?tab=Specifications (дата обращения 14.11.2013).

- 20. Cortex-A7 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-a/cortex-a7.php?tab=Specifications (дата обращения

- 21. Deep inside ARM's new Intel killer // The Register. Режим доступа:

- http://www.theregister.co.uk/2011/10/20/details on big little processing/ (дата обращения 14.11.2013).

- 22. Cortex-A8 Specification Summary // ARM Limited. Режим доступа: tp://arm.com/products/processors/cortex-a/cortex-a8.php?tab=Specifications (дата обр

- http://arm.com/products/processors/cortex-a/cortex-a8.php?tab=Specifications (дата обращения 14.11.2013).

- 23. Cortex-A12 Processor // ARM Limited. Режим доступа:

14.11.2013).

- http://www.arm.com/products/processors/cortex-a/cortex-a12-processor.php (дата обращения 14.11.2013).

- 24. Cortex-A15 Specification Summary // ARM Limited. Режим доступа: http://arm.com/products/processors/cortex-a/cortex-a15.php?tab=Specifications (дата обращения 14.11.2013).

- 25. Exclusive: ARM Cortex-A15 "40 Per Cent" Faster Than Cortex-A9 // ITProPortal.com. Режим доступа: http://www.itproportal.com/2011/03/14/exclusive-arm-cortex-a15-40-cent-faster-cortex-a9/ (дата обращения 14.11.2013).

- 26. Cortex-A53 Processor // ARM Limited. Режим доступа: http://www.arm.com/products/processors/cortex-a50/cortex-a53-processor.php (дата обращения 14.11.2013).

- 27. Cortex-A57 Processor // ARM Limited. Режим доступа: http://www.arm.com/products/processors/cortex-a50/cortex-a57-processor.php (дата обращения 14.11.2013).